Services

ChipDesign offers integrated circuit (IC) & sensor design services:

IC design

ChipDesign offers analog mixed-signal and RF / millimeter-wave (mmW) IC design services using silicon-based triple-well bulk and twin-well PD- and FD-SOI CMOS processes, BCD processes, and III-V compound semiconductor D/E-mode InGaAs pHEMT and GaN HEMT processes (interested in SiGe:C HBT and InP DHBT processes), covering:

- Specification: design trade-offs using chain analysis based partitioning (Mathworks MATLAB & Simulink, Verilog-AMS)

- IC design: schematic entry and layout (Cadence Virtuoso and Mentor Graphics S-Edit/L-Edit)

- Analog design: analysis and design of comparators (clocked, hysteretic), level shifters, single-ended output and fully-differential opamps, reference oscillators (crystal, relaxation, ring), temperature sensors (CTAT, PTAT), voltage references (bandgap reference, VTH reference), voltage regulators (HDO, LDO). Frequency compensation of circuits using negative feedback (Ahuja, Miller, resistor or super source follower insertion). Offset minimization (chopping, auto-zeroing, correlated double sampling). High-speed techniques (pre-charge) (Cadence Spectre/APS, Mentor Graphics Eldo, ngspice, interested in Synopsys HSPICE).

- Electromagnetic design: on-chip antenna and passives (balun, coupler, inductor, transformer) design with 2.5D MoM solvers (Integrand EMX, Keysight Momentum, Sonnet).

- High-voltage design: gate driver design, voltage multiplier rectifier design (AC-DC). Interested in charge pump and LC and SC DC-DC converter design (buck, boost).

- Mixed-signal design:

- ADC and DAC design: high-accuracy ADC design (SAR, CT and DT sigma-delta), high-speed ADC design (flash, pipeline), DAC design (switched capacitor charge redistribution, current steering). Interested in DDS design. Optimization of accuracy, offset & gain error, INL & DNL, SNR & SFDR.

- PLL and synthesizer design: mixed-signal PLL based integer-N and fractional-N synthesizer (PFD, CP, LPF, VCO, prescaler, MMD, MASH (in case of fractional-N synthesizer)). I/Q dividers for 4/8-phase LO distribution. Interested in ADPLL design. Jitter minimization through retiming.

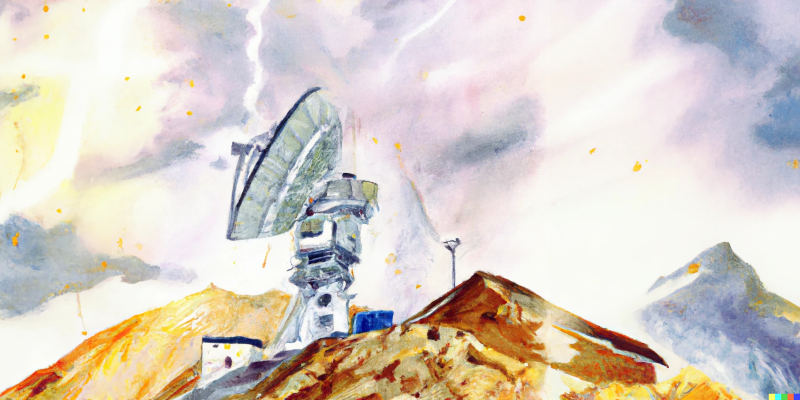

- RF/mmW transceiver design: design of passive (antenna matching tuner, attenuator, mixer, (TTD) phase shifter, SPNT switch) and active (multiplier, LNA, PA, TIA, VCO) circuits. Analysis of non-linear RF circuits and cyclostationary noise (phase noise, jitter) with HB and (Q)PSS solvers (Cadence Spectre/RF, Keysight GoldenGate, Mentor Graphics Eldo).

- IC floor planning for minimal IR drops, L*di/dt kicks and maximal thermal conduction. Isolation of ground domains in order to prevent coupling of noise and spurs. ESD-proof pad ring design.

Sensor design

ChipDesign also provides capacitive and piezoelectric MEMS device (accelerometers, gyroscopes, inertial measurement units, microphones, resonators, switches) design services.